# **NNCI Annual Meeting**

# 27 October 2023

Trevor Thornton (Arizona State University), Shyam Aravamudhan (North Carolina A&T State University), Mary Tang (Stanford), Sanjay Banerjee (UT Austin), Philip Wong (Stanford)

$\mathsf{TNF}$

# Virtual workshop held in September 2022

Microelectronics/ Semiconductor Research Community Virtual Workshop

September 8 and 9, 2022 12pm - 3:30 pm EDT

Hosted by NSF National Nanotechnology Coordinated Infrastructure (NNCI) Program

Organizers: Philip Wong (Stanford), Trevor Thornton (Arizona State), Shyam Aravamudhan (North Carolina A&T Univ.) and Sanjay Banerjee (Univ. of Texas)

"The anticipated outcome of this workshop will be developing a report that could inform CHIPS funding as it relates to USICA, NSTC, NAMP and the Microelectronics Commons, as well as NSF Engines and FuSe".

## Report published December 2022

#### MICROELECTRONICS/SEMICONDUCTOR RESEARCH COMMUNITY NSF NNCI WORKSHOP REPORT

Sanjay Banerjee (Univ. of Texas), Philip Wong (Stanford), Trevor Thornton (ASU),

Shyam Aravamudhan (NCA&T) and Sara Ostrowski (Stanford)

SEPTEMBER 9, 2022

Appendices

- TCAD (Victor Moroz, Fellow Synopsys)

- EDA (Prith Banerjee, CTO, Ansys)

- American Semiconductor Academy (Tsu-Jae King Liu, Dean UC Berkeley)

- NNCI Overview (Oliver Brand, Georgia Tech)

- Role of Universities (Jesus Del Alamo, MIT)

- Shaping the Future: Intel's Academic Collaborations (Gabriela Cruz Thompson and Sowmya Venkataramani, Intel)

- Workforce Development Overview (Peter Bermel, Purdue University)

- Workforce Development Panel (Patrick Govang, Cornell University)

#### White Paper: Microelectronics/Semiconductor Research Community Virtual Workshop

#### SUMMARY

In response to the recent efforts of the federal government to bolster US semiconductor manufacturing under the auspices of the CHIPS Act, the NSP's National Nanotechnology Coordinated Infrastructure (NNCI) held a two-day virtual workshop to examine how the NNCI can address various components of the CHIPS initiative.

The global semiconductor market is currently over \$600B, with an annual growth rate of ~10%, and will drive a \$31 electronics market by the end of decade. The US share of this market has fallen to less than 10%, which has clear economic and defense ramifications. This was the impetus for Congress to pass the \$52B CHIPS legislation to encourage in-shoring of semiconductor fabs.

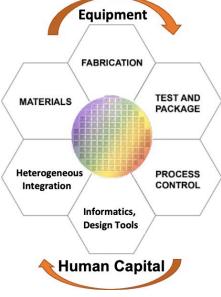

The first day of the workshop was devoted to invited talks by industry leaders who discussed the state of the art in their respective fields, and research challenges, highlighting opportunities for academic research. In the morning session, Dr. Kavalieros from Intel focused on advanced transistors for logic applications, Dr. Ramaswamy from Micron discussed advanced memory architectures, and Dr. Narayanan from IBM educated the attendees about heterogeneous integration (HI) as the next paradigm in Moore's law and Dennard scaling. Some of the common themes that emerged are the move toward next-generation 3D devices such as nanosheet transistors, and 2.5D and 3D HI of chiplets of CPU, GPU, high bandwidth DRAMs, and non-volatile memory using hybrid bonding with sub-10 micron pitc for applications such AI/ML using neuromorphic computing. Power management becomes a huge challenge in such 3D systems.

In the afternoon session, Dr. Chudzik from Applied Materials discussed equipment challenges for 300 mm tools which need to handle a wider set of materials, semiconductors beyond Si such as SiC and GaN, and advanced packaging. Dr. Moroz from Synopsys and Dr. Banerjee from Ansys discussed TCAD and EDA challenges, respectively. Moroz pointed out the need for more *ab-initio* simulation methodologies such as density functional theory (DFT) for structure calculations, coupled with non-equilibrium Green's function (NEGF) methodologies for electronic transport, which go beyond the usual drift-diffusion based simulators. Dr. Banerjee pointed out the need to do multi-physics simulations for HI, involving coupled heat and charge transport, as well as high speed simulation of Maxwell's equations to handle parasitics.

The industry overviews on the first day set the stage for sessions on the second day related to workforce development and academic infrastructure. For CHIPS legislation to be impactful, there must be significant renewal of aging academic microelectronics, R&D infrastructure, and a

RIVV

# Report published December 2022

White Paper: Microelectronics/Semiconductor Research Community Virtual Workshop

#### 6: CONCLUSIONS / FUTURE DIRECTIONS

A key question that this workshop attempted to answer was how to revamp the aging academic cleanrooms. For example, what wafer size should universities target in the future, and how would these more expensive facilities be maintained? It may make sense to use CHIPS funding to build on the extremely successful NNCI model to expand the capabilities and geographical reach of NNCI. It was concluded that academic cleanrooms should not invest in 12-inch capability because of the equipment and operating costs. 8" may be the "sweet spot" where leading edge tools can be acquired and maintained at a sustainable cost. However, smaller wafer sizes such as 6" may also be a viable option for TRL 1 level work done by universities.

Microelectronics Commons 'Request for Solutions' announced November 2022 with proposals due in February 2023

Technology Areas Supported by the Microelectronics Commons

# Eight regional Hubs announced in September

nano@stanford

# The Microelectronics Commons Hubs

The Microelectronics Commons program comprises eight regional Hubs, each focused on multiple technology areas and supported by their network of commercial innovators. If you are interested in learning more, <u>register</u> for the Microelectronics Commons Annual Meeting in Washington, D.C.

| Applied Research<br>Institute<br>Silicon Crossroads<br>Microelectronics<br>ommons (SCMC) Hub      | AZ Board of Regents<br>on behalf of Arizona<br>State University<br>Southwest Advanced<br>Prototyping (SWAP) Hub | The Board of Trustees<br>of the Leland Stanford<br>Junior University<br>California-Pacific-<br>Northwest AI Hardware<br>Hub (Northwest-AI-Hub)             | Massachusetts<br>Technology<br>Collaborative<br>Northeast<br>Microelectronics Coalition<br>(NEMC) Hub                               |

|---------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| Midwest<br>Microelectronics<br>Consortium<br>The Midwest<br>Microelectronics<br>Consortium (MMEC) | North Carolina State<br>University<br>Commercial Leap Ahead<br>for Wide-bandgap<br>Semiconductors (CLAWS)       | The Research<br>Foundation for SUNY,<br>acting on behalf of<br>SUNY Polytechnic<br>Institute<br>Northeast Regional<br>Defense Technology Hub<br>(NORDTECH) | University of Southern<br>California<br>California Defense Ready<br>Electronics and<br>Microdevices Superhub<br>(California DREAMS) |

# The Microelectronics Commons Hubs

- The Northeast Microelectronics Coalition Hub. This hub is led by the Massachusetts Technology Collaborative in Massachusetts, has 90 hub members, and has been awarded \$19.7 million.

- The Silicon Crossroads Microelectronics Commons Hub. This hub is led by the Applied Research Institute in Indiana, has 130 hub members, and has been awarded \$32.9 million.

- The California Defense Ready Electronics and Microdevices Superhub Hub. This hub is led by the University of Southern California in California, has 16 hub members and has been awarded \$26.9 million.

- The Commercial Leap Ahead for Wide Bandgap Semiconductors Hub. This hub is led by the North Carolina State University in North Carolina, has seven hub members and has been awarded \$39.4 million.

https://www.defense.gov/News/News-Stories/Article/Article/3532338/dod-names-8-locations-to-serve-as-newmicroelectronics-commons-hubs/

# The Microelectronics Commons Hubs

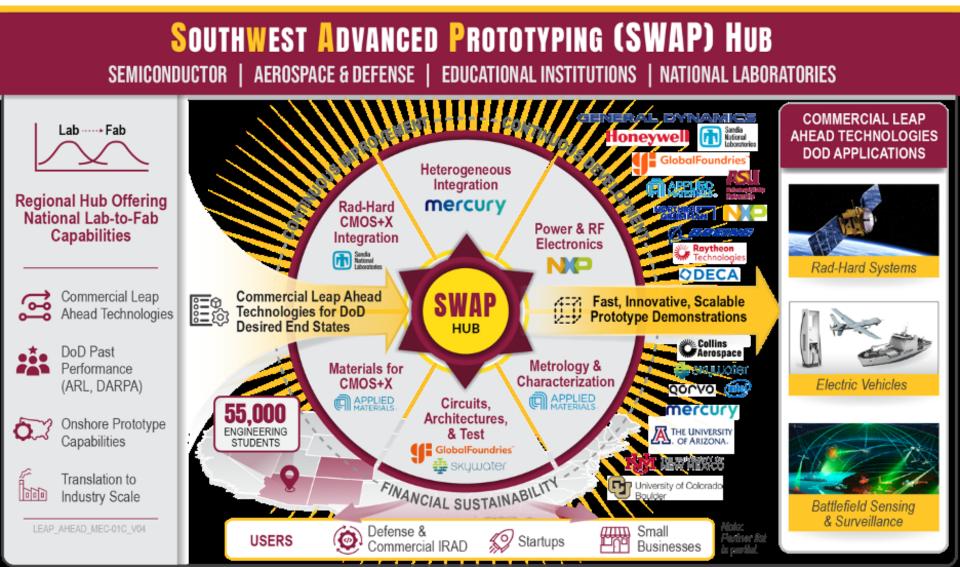

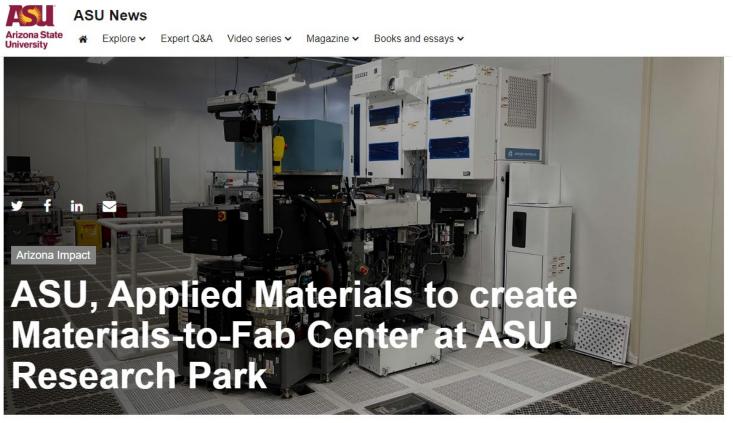

- The Southwest Advanced Prototyping Hub. This hub is led by the Arizona Board of Regents on behalf of Arizona State University in Arizona, has 27 hub members and has been awarded \$39.8 million.

- The Midwest Microelectronics Consortium Hub in Ohio. This hub has 65 hub members and has been awarded \$24.3 million.

- The Northeast Regional Defense Technology Hub. This hub is led by the Research Foundation for the State University of New York in New York, has 51 hub members, and has been awarded \$40 million.

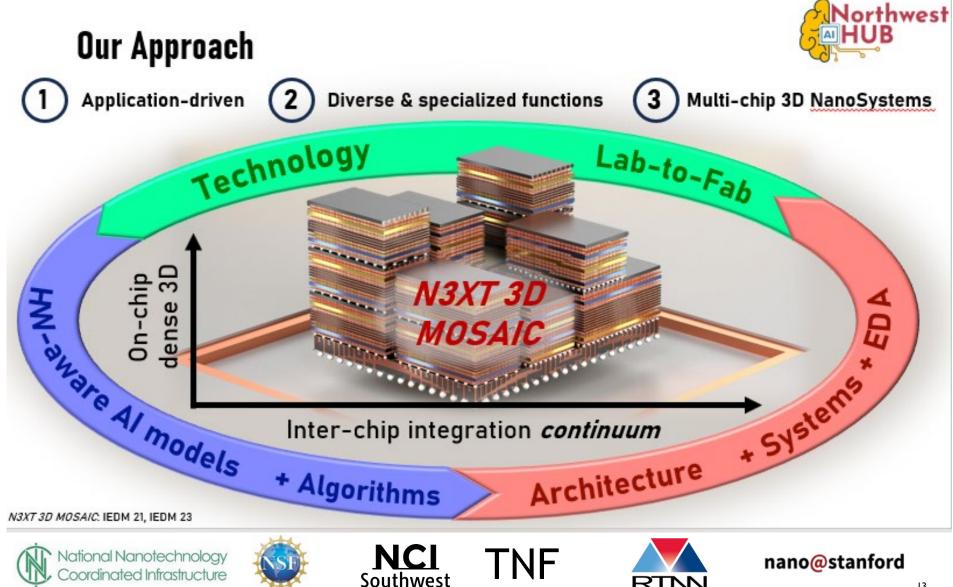

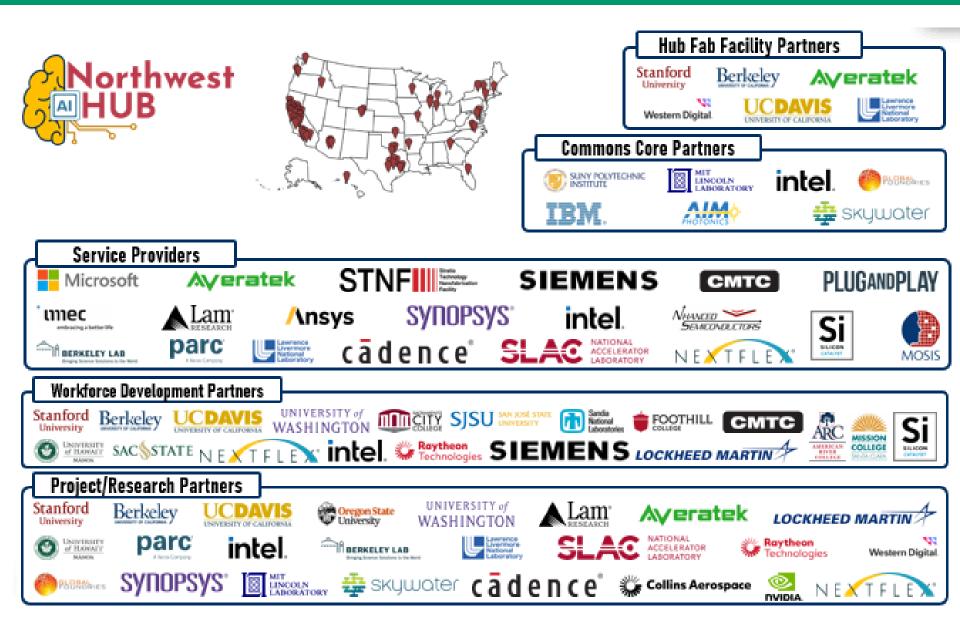

- The California-Pacific-Northwest AI Hardware Hub. This hub is led by the Board of Trustees of the Leland Stanford Junior University in California, has 44 hub members, and has been awarded \$15.3 million.

https://www.defense.gov/News/News-Stories/Article/Article/3532338/dod-names-8-locations-to-serve-as-newmicroelectronics-commons-hubs/

# ASU SWAP Hub

## **ASU SWAP Hub**

July 11, 2023

More than \$270M in corporate, state investment will help advance Arizona's semiconductor industry

ford

# CLAWS Hub NC State, NC A&T State, Coherent, Wolfspeed, General Electric, Bluglass, Adroit Materials, Kyma

Epitaxy

#### Wide Bandgap Semiconductor Research Foundry

Provide Low-Cost Agility in Semiconductor Development

Establish Critical Technology Roadmaps Keep Constant Pulse on State of the Art Identify and Leverage Synergies Workforce with Technical Literacy

III- Nitride Electronics Ultra Wide Bandgap Electronics

The desired end state is the lab-to-fab maturation of materials, devices, architectures, and processes to provide and/or enable revolutionary capabilities

TNF

## **CLAWS Hub - Workforce Development**

Proposed that Education and Workforce Efforts Scale with Prototype Projects to ensure relevance, involvement and sustainment of workforce activities.

Present Project Supports/Anticipates:

- Summer Programs at NCSU, NC A&T

- Specialized Short Courses

- Expanded Course involvement

- Community College Involvement

- Undergraduate Research

- Engagement with DOD SMART Fellowship Program.

- Outreach to K-12

- Intensive Training > 100 students/yea

- Exposure to Semiconductor Career opportunities > 1000 students/year.

#### Existing Workforce Development and Outreach Efforts Research Foundry Creates Symbiotic Opportunity to Train Workforce

- Community College Trains the Trainer (Images this slide)

- Collaborate with Durham Tech., training Wolfspeed Technicians

- PowerAmerica Workshops, Equipment Short Courses

- 4 Undergrad and Graduate Courses with hands-on clean room

- Undergrad Work Study students assist in clean room operations

- Internships with Wolfspeed, other semiconductor companies

- Strong demand for NC State Students by Industry

- Undergrad research opportunities

#### Leveraging:

- NC A&T HBCU Expertise

- North Carolina Community College partnerships

- Regional Innovation Networks

- Industry Partners

Co-development of workforce

Rankings & Metrics

Office of Research

800

#### nano@stanford

Inventior

# Q&A